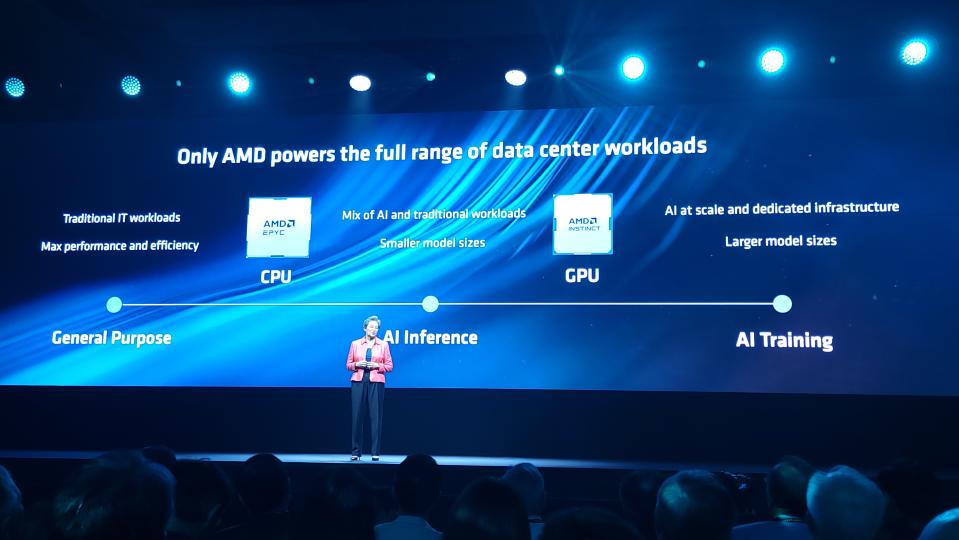

AMD’s hotly anticipated 5th-Gen EPYC Turin processors will launch in the second half of 2024, Lisa Su announced during her Computex 2024 keynote. The 3nm chips mark the debut of AMD’s Zen 5 architecture for data center chips, and AMD claims they are up to 5.4x faster than Intel’s competing current-gen Xeon chips in key AI workloads.

Turin comes in two variants: one with up to 128 standard Zen 5 cores and another using density-optimized CPU cores called Zen 5c — that model stretches up to 192 cores. Su also announced that AMD now has 33% of the data-center market.

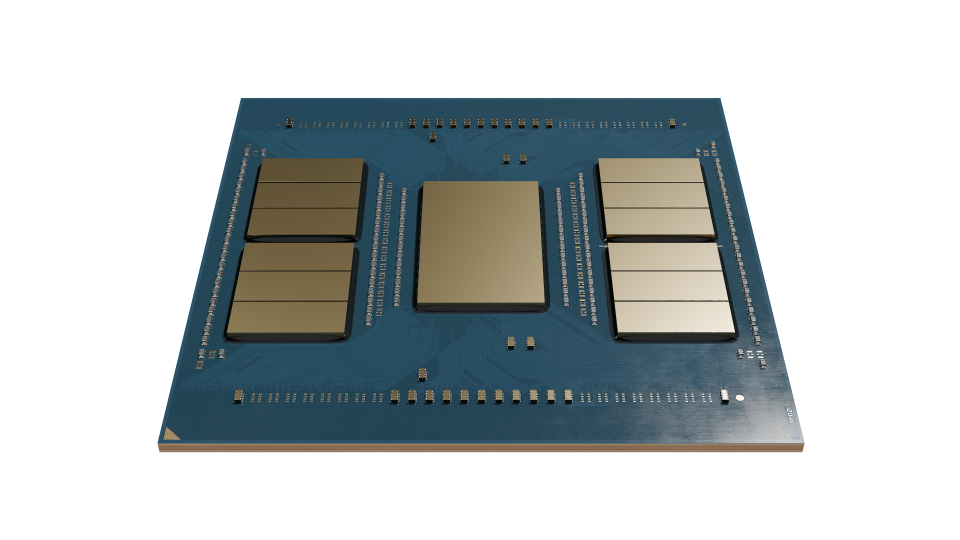

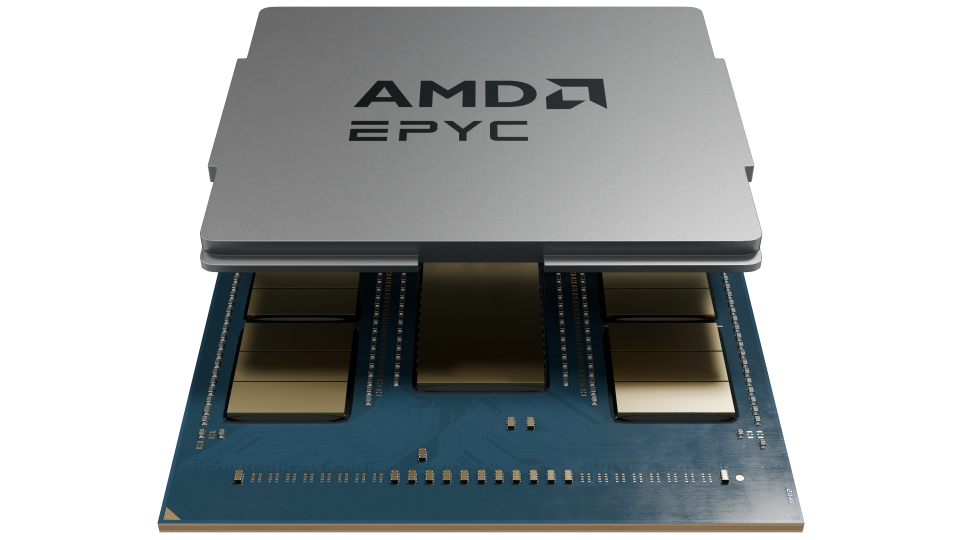

The new Zen 5c-powered chips will feature up to 192 cores and 384 threads fabbed on the 3nm process node, then paired with a 6nm I/O Die (IOD) crammed into a single socket. The chip is comprised of 17 chiplets. The highest core count models utilize AMD’s Zen 5c architecture, which uses density-optimized cores that are conceptually similar to Intel’s e-cores. However, AMD pioneered this core type for x86 chips in the data center.

The models with standard full-performance Zen 5 cores come with 12 compute dies with the N4P process node and one central 6nm IOD die, for a total of 13 chiplets.

AMD displayed a spate of benchmarks against Intel’s competing Xeon chips, but as with all vendor-provided benchmarks, take them with some salt. AMD claims an up to 5.4X advantage in an LLM AI model (chatbots) over Xeon, along with a 2.5X advantage in translation models and a 3.9X advantage in summarization work. AMD also showed a 3.1x advantage in the scientific NAMD workload with its 128-core Turin model and a live demo of Turin delivering 4X more tokens per second than Xeon.

The 192-core Zen 5c chips are the follow-on series to AMD’s EPYC Bergamo, the industry’s first x86 data center processor with density-optimized cores (Zen 4c). Bergamo tops out at 128 cores.

The ‘standard’ Turin models with the Zen 5 architecture stretch to 128 cores, marking a strong generational gain over the current-gen EPYC Genoa, which peaks at 96 cores.

AMD’s 192-core EPYC Turin chips are designed for the highest core density. They have an optimized Zen 5c core that halves the area needed for each core yet supports the same features as the full-fat Zen 5 cores, making them exceedingly attractive to hyperscalers (AMD says it owns 50% of this market segment).

The Zen 5c Turin chips will compete with Intel’s 144-core Sierra Forest chips, which mark the debut of Intel’s Efficiency cores (E-cores) in its Xeon data center lineup, and Ampre’s 192-core AmpereOne processors, not to mention the custom silicon being developed or employed by Google and Microsoft.

Meanwhile, the standard Zen 5 EPYC processors will take on Intel’s coming Xeon 6 lineup. Turin will drop into motherboards with the same SP5 socket used for 4th-Gen EPYC Genoa and Bergamo, allowing the existing kit to be simply upgraded to a drastically faster chip. This tactic also speeds quals on newer motherboards and servers, thus enabling a quicker time to market.

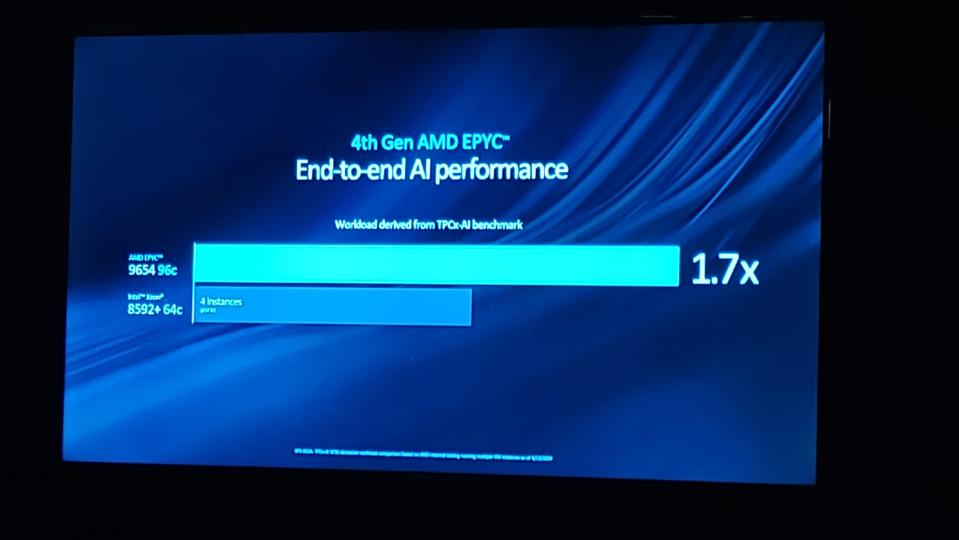

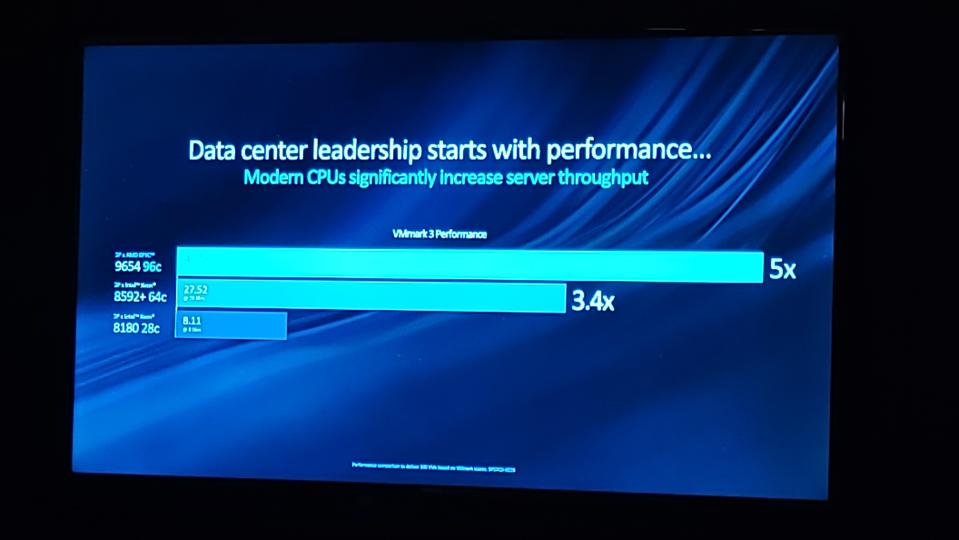

AMD also shared some benchmarks highlighting its claimed advantages in AI workloads with its existing 4th-Gen EPYC chips over competing Intel models. We expect more details to emerge as the Turin chips move closer to the market.

Signup bonus from